基于神经网络的预取研究开题报告

2020-02-18 17:00:22

1. 研究目的与意义(文献综述)

1.1 目的及意义

随着计算机制造技术的发展和计算机系统结构的创新,计算机的性能不断的提高,尤其在20世纪70年代末到80年代初,大规模集成电路和微处理器的出现使计算机性能的年增长速度提高到了约35%,我们所熟知的摩尔定律揭示了计算机性能的的发展,从1986年以后,处理器的速度的发展平均每年提高50%,现如今的计算机的cpu已经由过去的mhz变为如今的ghz,然而由于制造工艺的不同,存储器的速度平均每年提升7%,长期的积累导致处理器和存储器的速度差异越来越大,不均衡的发展速度造成了内存提取速度严重滞后于处理器的计算速度,这样就导致处理器的性能无法完全发挥出来,这就是被称为“内存墙”问题,为了缓解这个问题,利用程序访问的局部性原理,微处理器采用了分层存储系统,引入了cache,在最靠近cpu的内存速度最快,容量小,快到与cpu速度匹配,离cpu远的内存速度慢,容量大,cache的引入极大提高了存储器的访存效率,但是由于容量小,总有一些数据不会被直接捕获,这就是未命中,因此采用预取技术,这是为了当cpu需要读取数据时,能够直接从cache中提取,预取技术能够极大的提高命中率,

而神经网络是一种解决预测问题强有力的技术,在自然语言处理与文本理解中有着极大的应用,我将对基于序列的神经网络与微处理器进行结合,目的构建出有效的预取机制,研究其中的预取技术来进一步提高命中率,能够实现计算机性能的提升。

2. 研究的基本内容与方案

2.1基本内容

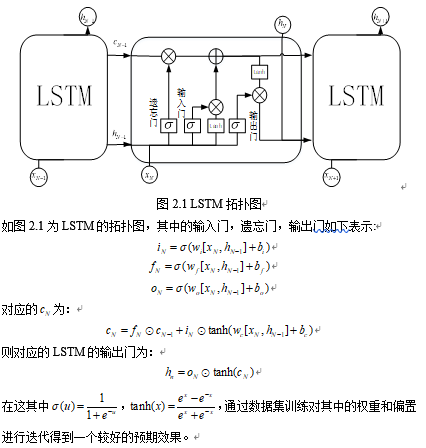

神经网络已经成为了许多序列测试的首选模型,而其中lstm(longshort-term memory)是一种时间递归神经网络,它适合处理和预测时间序列中间间隔和延迟相对较长的事件,它有着输入门,遗忘门和输出门,只有符合算法认证的信息才会留下,不符的信息通过遗忘门被遗忘掉。

2.2 目标

3. 研究计划与安排

1~3周:查阅相关文献资料,明确研究方向,确定研究内容,完成开题报告;

4~6周:完成缓存访问序列的分析;

7~9周:完成预取方案的设计;

4. 参考文献(12篇以上)

[1]hashemi m, swersky k, smith j a, etal. learning memory access patterns. 2018.

[2]张凌峰. 多核处理器共享级cache访存行为建模[d].南京:东南大学, 2017

[3]范瑞. 基于android的移动云存储缓存预取算法研究[d]. 武汉:华中科技大学, 2016.